A indústria eletrônica está se aproximando do limite do número de transistores que podem ser colocados na superfície de um chip de computador. Portanto, os fabricantes de chips estão procurando crescer em vez de sair.

Em vez de comprimir transistores cada vez menores em uma única superfície, a indústria pretende empilhar múltiplas superfícies de transistores e elementos semicondutores – o mesmo que transformar uma casa de fazenda em um arranha-céu. Esses chips multicamadas poderiam lidar com exponencialmente mais dados e executar funções muito mais complexas do que a eletrônica atual.

Um obstáculo significativo, entretanto, é a plataforma na qual os chips são construídos. Hoje, volumosos wafers de silício servem como a principal estrutura na qual são cultivados elementos semicondutores monocristalinos de alta qualidade. Qualquer chip empilhável teria que incluir um “piso” espesso de silício como parte de cada camada, retardando qualquer comunicação entre camadas semicondutoras funcionais.

Agora, os engenheiros do MIT encontraram uma maneira de contornar esse obstáculo, com um design de chip multicamadas que não requer nenhum substrato de wafer de silício e funciona em temperaturas baixas o suficiente para preservar o circuito da camada subjacente.

Em um estudo aparecendo hoje no jornal Naturezaa equipe relata o uso do novo método para fabricar um chip multicamadas com camadas alternadas de materials semicondutor de alta qualidade cultivadas diretamente umas sobre as outras.

O método permite que os engenheiros construam transistores de alto desempenho, memória e elementos lógicos em qualquer superfície cristalina aleatória – não apenas na volumosa estrutura de cristal dos wafers de silício. Sem esses substratos espessos de silício, múltiplas camadas semicondutoras podem estar em contato mais direto, levando a uma comunicação e computação melhores e mais rápidas entre as camadas, dizem os pesquisadores.

Os pesquisadores prevêem que o método poderia ser usado para construir {hardware} de IA, na forma de chips empilhados para laptops ou dispositivos vestíveis, que seriam tão rápidos e poderosos quanto os supercomputadores atuais e poderiam armazenar enormes quantidades de dados, equivalentes aos knowledge facilities físicos.

“Esta inovação abre um enorme potencial para a indústria de semicondutores, permitindo que os chips sejam empilhados sem limitações tradicionais”, diz o autor do estudo Jeehwan Kim, professor associado de engenharia mecânica no MIT. “Isso poderia levar a melhorias de ordens de grandeza no poder de computação para aplicações em IA, lógica e memória.”

Os coautores do estudo no MIT incluem o primeiro autor Ki Seok Kim, Seunghwan Search engine optimisation, Doyoon Lee, Jung-El Ryu, Jekyung Kim, Jun Min Suh, June-chul Shin, Min-Kyu Tune, Jin Feng e Sangho Lee, junto com colaboradores do Samsung Superior Institute of Expertise, da Universidade Sungkyunkwan na Coreia do Sul e da Universidade do Texas em Dallas.

Bolsões de sementes

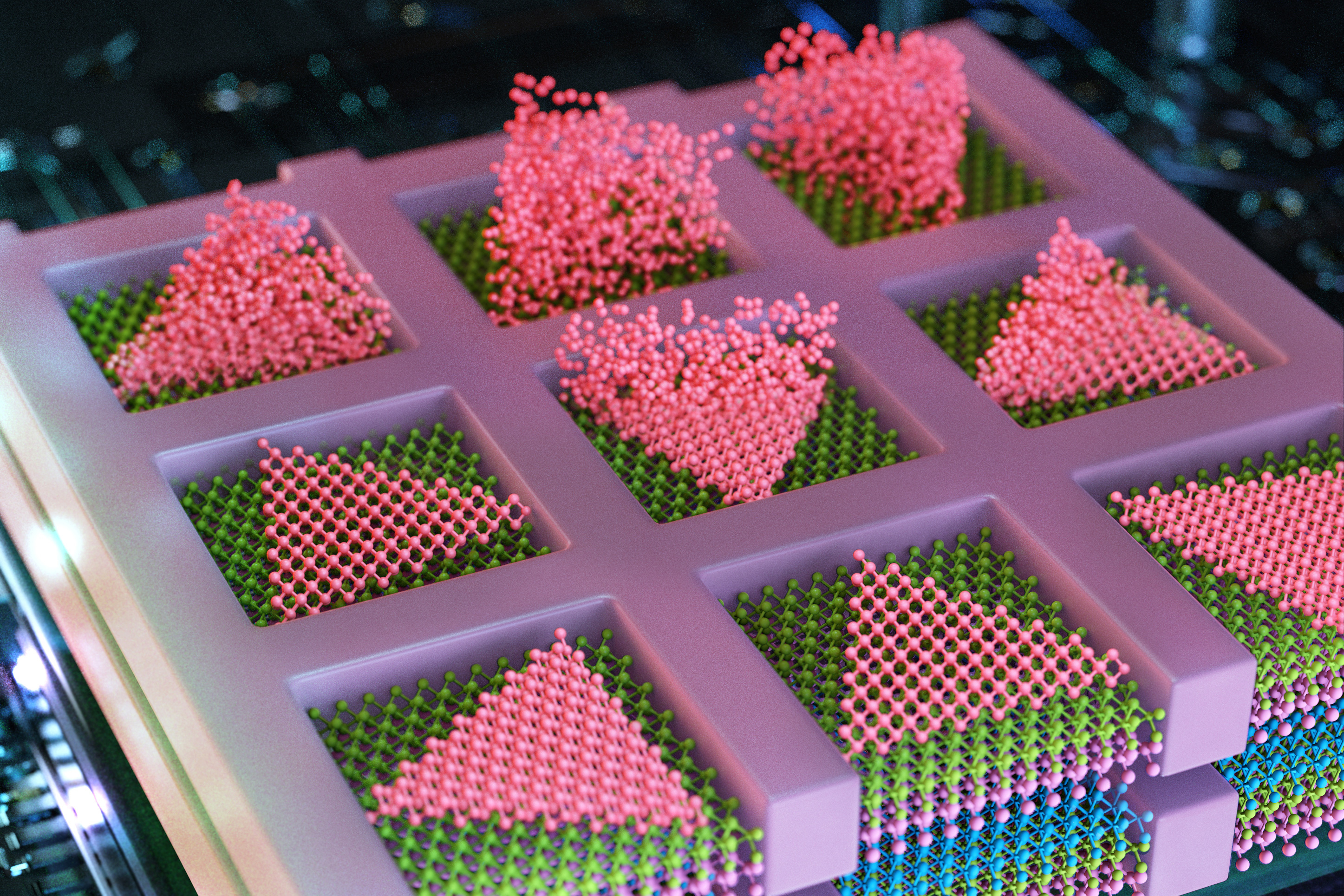

Em 2023, o grupo de Kim relatado que eles desenvolveram um método para cultivar materiais semicondutores de alta qualidade em superfícies amorfas, semelhante à topografia diversificada de circuitos semicondutores em chips acabados. O materials que eles cultivaram period um tipo de materials 2D conhecido como dichalcogenetos de metais de transição, ou TMDs, considerado um sucessor promissor do silício para a fabricação de transistores menores e de alto desempenho. Esses materiais 2D podem manter suas propriedades semicondutoras mesmo em escalas tão pequenas quanto um único átomo, enquanto o desempenho do silício se degrada drasticamente.

Em seu trabalho anterior, a equipe desenvolveu TMDs em wafers de silício com revestimentos amorfos, bem como sobre TMDs existentes. Para encorajar os átomos a se organizarem em uma forma monocristalina de alta qualidade, em vez de uma desordem policristalina aleatória, Kim e seus colegas primeiro cobriram uma pastilha de silício em uma película muito fina, ou “máscara” de dióxido de silício, com a qual eles modelaram. pequenas aberturas ou bolsos. Eles então fizeram fluir um gás de átomos sobre a máscara e descobriram que os átomos se depositavam nos bolsos como “sementes”. Os bolsões confinavam as sementes para crescerem em padrões regulares e monocristalinos.

Mas na época, o método só funcionava a cerca de 900 graus Celsius.

“Você tem que cultivar esse materials monocristalino abaixo de 400 Celsius, caso contrário, o circuito subjacente ficará completamente cozido e arruinado”, diz Kim. “Então, nosso dever de casa foi que tínhamos que fazer uma técnica semelhante em temperaturas inferiores a 400 Celsius. Se pudéssemos fazer isso, o impacto seria substancial.”

Construindo

Em seu novo trabalho, Kim e seus colegas procuraram ajustar seu método para cultivar materiais 2D monocristalinos em temperaturas baixas o suficiente para preservar qualquer circuito subjacente. Eles encontraram uma solução surpreendentemente simples na metalurgia – a ciência e a arte da produção de steel. Quando os metalúrgicos despejam steel fundido em um molde, o líquido lentamente “nuclea” ou forma grãos que crescem e se fundem em um cristal com padrão common que endurece na forma sólida. Os metalúrgicos descobriram que esta nucleação ocorre mais facilmente nas bordas de um molde no qual o steel líquido é derramado.

“Sabe-se que a nucleação nas bordas requer menos energia — e calor”, diz Kim. “Portanto, pegamos emprestado esse conceito da metalurgia para utilizá-lo em futuros hardwares de IA.”

A equipe procurou cultivar TMDs monocristalinos em um wafer de silício que já foi fabricado com circuitos de transistor. Eles primeiro cobriram o circuito com uma máscara de dióxido de silício, assim como em trabalhos anteriores. Eles então depositaram “sementes” de TMD nas bordas de cada um dos bolsos da máscara e descobriram que essas sementes nas bordas cresceram em materials monocristalino em temperaturas tão baixas quanto 380 graus Celsius, em comparação com sementes que começaram a crescer no centro, longe de as bordas de cada bolsa, o que exigiu temperaturas mais altas para formar materials monocristalino.

Indo um passo além, os pesquisadores usaram o novo método para fabricar um chip multicamadas com camadas alternadas de dois TMDs diferentes – dissulfeto de molibdênio, um candidato promissor a fabric para a fabricação de transistores do tipo n; e disseleneto de tungstênio, um materials que tem potencial para ser transformado em transistores do tipo p. Ambos os transistores do tipo p e n são os blocos de construção eletrônicos para realizar qualquer operação lógica. A equipe conseguiu cultivar ambos os materiais na forma monocristalina, diretamente um sobre o outro, sem a necessidade de pastilhas de silício intermediárias. Kim diz que o método irá efetivamente dobrar a densidade dos elementos semicondutores de um chip e, particularmente, do semicondutor de óxido metálico (CMOS), que é um bloco de construção básico de um circuito lógico moderno.

“Um produto realizado por nossa técnica não é apenas um chip lógico 3D, mas também uma memória 3D e suas combinações”, diz Kim. “Com nosso método 3D monolítico baseado em crescimento, você poderia aumentar de dezenas a centenas de camadas lógicas e de memória, umas sobre as outras, e elas seriam capazes de se comunicar muito bem.”

“Os chips 3D convencionais foram fabricados com wafers de silício no meio, fazendo furos no wafer – um processo que limita o número de camadas empilhadas, resolução de alinhamento vertical e rendimentos”, acrescenta o primeiro autor Kiseok Kim. “Nosso método baseado no crescimento aborda todas essas questões de uma só vez.”

Para comercializar ainda mais seu design de chip empilhável, Kim criou recentemente uma empresa, FS2 (Future Semiconductor 2D supplies).

“Até agora mostramos um conceito em conjuntos de dispositivos de pequena escala”, diz ele. “O próximo passo é ampliar para mostrar a operação profissional do chip de IA.”

Esta pesquisa é apoiada, em parte, pelo Samsung Superior Institute of Expertise e pelo Escritório de Pesquisa Científica da Força Aérea dos EUA.